# SPICE Device Model Si1050X Vishay Siliconix

### N-Channel 20-V (D-S) MOSFET

### **CHARACTERISTICS**

- N-Channel Vertical DMOS

- Macro Model (Subcircuit Model)

- Level 3 MOS

- Apply for both Linear and Switching Application

- Accurate over the -55 to 125°C Temperature Range

- Model the Gate Charge, Transient, and Diode Reverse Recovery Characteristics

### **DESCRIPTION**

The attached spice model describes the typical electrical characteristics of the n-channel vertical DMOS. The subcircuit model is extracted and optimized over the -55 to  $125^{\circ}$ C temperature ranges under the pulsed 0-V to 4.5-V gate drive. The saturated output impedance is best fit at the gate bias near the threshold voltage.

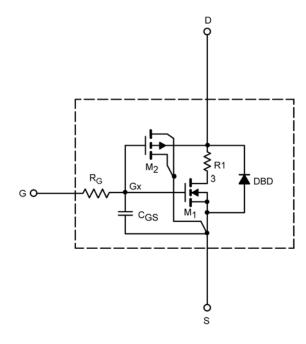

A novel gate-to-drain feedback capacitance network is used to model the gate charge characteristics while avoiding convergence difficulties of the switched  $C_{\rm gd}$  model. All model parameter values are optimized to provide a best fit to the measured electrical data and are not intended as an exact physical interpretation of the device.

### SUBCIRCUIT MODEL SCHEMATIC

This document is intended as a SPICE modeling guideline and does not constitute a commercial product data sheet. Designers should refer to the appropriate data sheet of the same number for guaranteed specification limits.

# **SPICE Device Model Si1050X**

# Vishay Siliconix

| SPECIFICATIONS (T <sub>J</sub> = 25°C UN      | NLESS OTHER\        | WISE NOTED)                                                             |                   |                  |              |

|-----------------------------------------------|---------------------|-------------------------------------------------------------------------|-------------------|------------------|--------------|

| Parameter                                     | Symbol              | Test Condition                                                          | Simulated<br>Data | Measured<br>Data | Unit         |

| Static                                        |                     |                                                                         |                   |                  |              |

| Gate Threshold Voltage                        | $V_{GS(th)}$        | $V_{DS} = V_{GS}$ , $I_{D} = 250 \mu A$                                 | 0.58              |                  | V            |

| On-State Drain Current <sup>a</sup>           | I <sub>D(on)</sub>  | $V_{DS} \le 5 \text{ V}, V_{GS} = 4.5 \text{ V}$                        | 56                |                  | Α            |

| Drain-Source On-State Resistance <sup>a</sup> | _                   | V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 1.34 A                        | 0.076             | 0.071            | Ω            |

|                                               | r <sub>DS(on)</sub> | $V_{GS} = 2.5 \text{ V}, I_D = 1.29 \text{ A}$                          | 0.083             | 0.078            |              |

|                                               |                     | V <sub>GS</sub> = 1.8 V, I <sub>D</sub> = 1.23 A                        | 0.093             | 0.085            |              |

| Forward Transconductance <sup>a</sup>         | g <sub>fs</sub>     | V <sub>DS</sub> = 4 V, I <sub>D</sub> = 1.34 A                          | 8                 | 4.12             | S            |

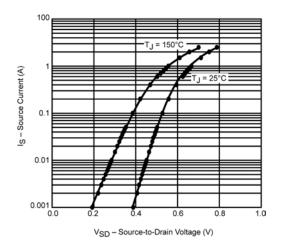

| Forward Voltage <sup>a</sup>                  | $V_{SD}$            | I <sub>S</sub> = 1 A                                                    | 0.86              | 0.80             | V            |

| Dynamic <sup>b</sup>                          | -                   |                                                                         |                   |                  | <del>-</del> |

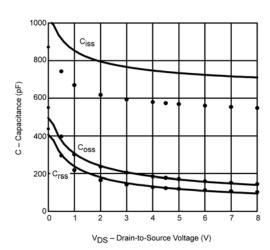

| Input Capacitance                             | C <sub>iss</sub>    | V <sub>DS</sub> = 4 V, V <sub>GS</sub> = 0 V, f = 1 MHz                 | 748               | 585              | pF           |

| Output Capacitance                            | C <sub>oss</sub>    |                                                                         | 185               | 190              |              |

| Reverse Transfer Capacitance                  | $C_{rss}$           |                                                                         | 132               | 130              |              |

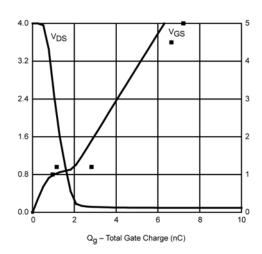

| Total Gate Charge                             | 0                   | $V_{DS}$ = 4 V, $V_{GS}$ = 5 V, $I_{D}$ = 1.34 A                        | 6.4               | 7.7              | nC           |

|                                               | Qg                  | V <sub>DS</sub> = 4 V, V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 1.34 A | 5.7               | 7.1              |              |

| Gate-Source Charge                            | Q <sub>gs</sub>     |                                                                         | 1.14              | 1.14             |              |

| Gate-Drain Charge                             | $Q_{gd}$            |                                                                         | 1.69              | 1.69             |              |

- a. Pulse test; pulse width  $\leq$  300  $\mu$ s, duty cycle  $\leq$  2%. b. Guaranteed by design, not subject to production testing.

# SPICE Device Model Si1050X Vishay Siliconix

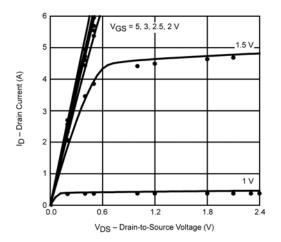

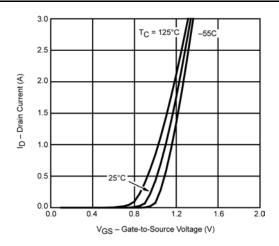

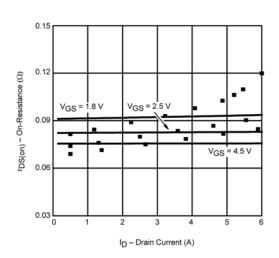

### COMPARISON OF MODEL WITH MEASURED DATA (TJ=25°C UNLESS OTHERWISE NOTED)

${}^{r}DS(on) - On-Resistance (\Omega)$

Note: Dots and squares represent measured data.

# **SPICE Device Model Si1050X**

# Vishay Siliconix

Vishay

### **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com